Hard skills are technical abilities, including skill in CAD software, understanding of materials science, and expertise in product design processes.

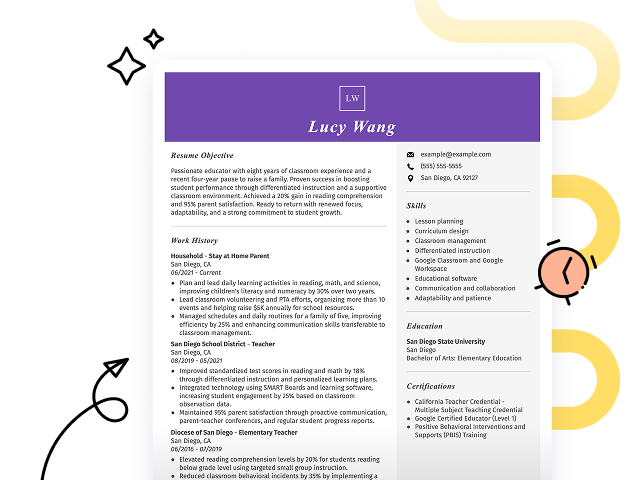

Popular Design Engineer Resume Examples

Discover our top design engineer resume examples that showcase key skills such as CAD skill, innovative problem-solving, and project management. These examples are crafted to help you effectively communicate your accomplishments in a competitive job market.

Ready to build your standout resume? Our Resume Builder offers user-friendly templates specifically designed for engineering professionals, making the process simple and efficient.

Recommended

Entry-level design engineer resume

This entry-level resume effectively highlights the job seeker's hands-on experience in product development and project management, showcasing significant accomplishments such as cost savings and efficiency improvements. New professionals in design engineering must demonstrate their technical skills, innovative capabilities, and teamwork experiences to attract employers despite limited professional history.

Mid-career design engineer resume

This resume effectively showcases the job seeker's qualifications by presenting measurable achievements and leadership roles. Clear examples of project impact and technical skills illustrate readiness for complex engineering challenges, reflecting significant career growth and expertise in design engineering.

Experienced design engineer resume

This resume illustrates the applicant's robust experience as a design engineer, emphasizing significant cost reductions of 15% and efficiency enhancements of 20%. The clear bullet-point format allows potential employers to quickly grasp the applicant's effective achievements.

Resume Template—Easy to Copy & Paste

Leila Gonzalez

Louisville, KY 40202

(555)555-5555

Leila.Gonzalez@example.com

Skills

- CAD Design

- Prototyping

- Finite Element Analysis (FEA)

- Project Management

- Product Development

- SolidWorks

- Cost Reduction Strategies

- Engineering Documentation

Languages

- German - Beginner (A1)

- French - Intermediate (B1)

- Spanish - Beginner (A1)

Professional Summary

Dynamic Design Engineer with 6 years of experience in CAD, prototyping, and FEA. Proven record of optimizing design processes, reducing costs, and driving $6M worth of projects. Expertise in SolidWorks, project management, and product development.

Work History

Design Engineer

Pinnacle Product Designs - Louisville, KY

November 2022 - October 2025

- Developed 20+ prototypes reducing design errors by 30%

- Optimized CAD processes achieving 25% resource savings

- Collaborated with cross-functional teams on M projects

Mechanical Design Specialist

Fusion Industrial Solutions - St. Matthews, KY

November 2019 - October 2022

- Designed 3D models improving product durability by 15%

- Led testing processes reducing defects by 18%

- Managed 2M design portfolio, ensuring client satisfaction

Junior Design Engineer

Innovatek Engineering Group - Shively, KY

November 2017 - October 2019

- Created CAD drafts improving workflow efficiency by 20%

- Supported development of 10+ engineering projects

- Implemented new tools reducing operational costs by 12%

Certifications

- Certified SolidWorks Professional (CSWP) - Dassault Systèmes

- Project Management Professional (PMP) - Project Management Institute

Education

Master of Science Mechanical Engineering

University of California, Berkeley Berkeley, California

May 2017

Bachelor of Science Mechanical Engineering

University of Illinois Urbana-Champaign Urbana, Illinois

May 2015

How to Write a Design Engineer Resume Summary

Your resume summary is the first thing employers will see, making it essential to create a strong opening that showcases your qualifications as a design engineer. This section should highlight your technical skills and innovative mindset, demonstrating how you can contribute to successful projects.

As a design engineer, you have the opportunity to emphasize your skill in CAD software, problem-solving abilities, and collaborative experience in engineering teams. These qualities are important for capturing the attention of hiring managers.

To guide you in crafting an effective resume summary, we’ll provide examples that illustrate what works well and what may fall short:

I am a skilled design engineer with experience in various projects. I am looking for a position where I can improve my skills and contribute to the team. A company that values innovation and creativity would be a perfect fit for me. I believe I can help achieve great results if hired.

- Contains broad statements about experience without mentioning specific skills or achievements

- Relies heavily on personal desires instead of highlighting what value the applicant brings to potential employers

- Uses weak language like 'skilled' and 'great results' without quantifiable examples or strong descriptors

Innovative design engineer with 7+ years of experience in product development and mechanical design, focusing on sustainable engineering solutions. Successfully led a project that reduced material costs by 20% while improving product performance through advanced modeling techniques. Proficient in CAD software, FEA analysis, and cross-functional team collaboration to drive innovative design processes.

- Begins with specific years of experience and area of expertise

- Highlights a quantifiable achievement that showcases cost savings and improved performance

- List relevant technical skills applicable to the engineering field

Pro Tip

Showcasing Your Work Experience

The work experience section is the cornerstone of your resume as a design engineer. This part will contain the bulk of your content, and good resume templates always emphasize this critical area.

It should be organized in reverse-chronological order, detailing your previous positions. Use bullet points to succinctly describe your key achievements and contributions to each role you’ve held.

Now, let’s look at a couple of examples that illustrate effective work history for design engineers. These examples will highlight what makes an entry strong and what pitfalls to avoid:

Design Engineer

ABC Engineering Corp – Seattle, WA

- Created designs for projects.

- Collaborated with team members.

- Used software tools for modeling.

- Assisted in project presentations.

- Lacks specific details about project outcomes

- Bullet points are too vague and do not highlight unique skills

- Emphasizes routine tasks rather than innovative contributions

Design Engineer

Tech Innovations Inc. – San Francisco, CA

March 2020 - Present

- Develop innovative product designs leading to a 30% reduction in production costs through optimized materials.

- Collaborate with cross-functional teams to improve design efficiency, achieving a 15% decrease in project turnaround time.

- Mentor junior engineers, fostering skill development and promoting best practices in design processes.

- Starts each bullet point with dynamic action verbs that clearly describe the applicant's contributions

- Incorporates quantifiable metrics that illustrate tangible impacts on productivity and cost savings

- Highlights relevant skills such as collaboration and mentorship that are important for the engineering field

While your resume summary and work experience play important roles, it's important to remember that other sections also deserve careful attention. For a more in-depth look at formatting all parts of your resume effectively, be sure to check out our complete guide on how to write a resume.

Top Skills to Include on Your Resume

A well-defined skills section is important for any design engineer's resume, as it quickly showcases your qualifications to potential employers. This area allows you to highlight your expertise and demonstrate that you possess the necessary competencies for the role.

For a design engineer, focus on both technical skills and software skill. Highlight tools like AutoCAD, SolidWorks, and MATLAB, which are essential for creating designs and simulations in engineering projects.

Soft skills, such as teamwork, problem-solving, and effective communication, help foster collaboration and innovation in engineering projects.

When selecting skills for your resume, it’s important to align them with what employers expect. Many organizations use applicant tracking systems (ATS) that filter out applicants lacking essential resume skills, so showcasing the right abilities can make a significant difference.

To ensure you're highlighting the most relevant skills, carefully review job postings in your field. These listings often contain valuable insights into which competencies are prioritized by recruiters and will help your resume stand out in both human reviews and ATS scans.

Pro Tip

10 skills that appear on successful design engineer resumes

To attract recruiters' attention, it's essential to highlight in-demand skills relevant to design engineering roles. Our resume examples showcase these important skills, empowering you to apply confidently and effectively.

Here are 10 key skills that can improve your resume if they align with your experience and job criteria:

Creative problem-solving

Attention to detail

Skill in CAD software

Project management

Collaboration and teamwork

Analytical thinking

Strong communication skills

Time management

Understanding of manufacturing processes

Knowledge of regulatory standards

Based on analysis of 5,000+ engineering professional resumes from 2023-2024

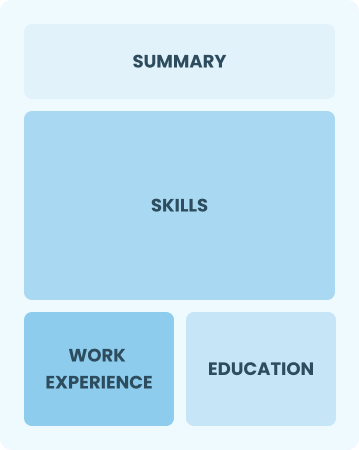

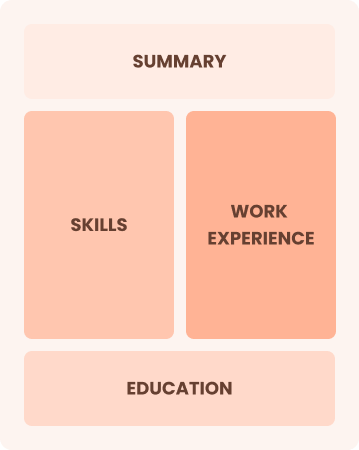

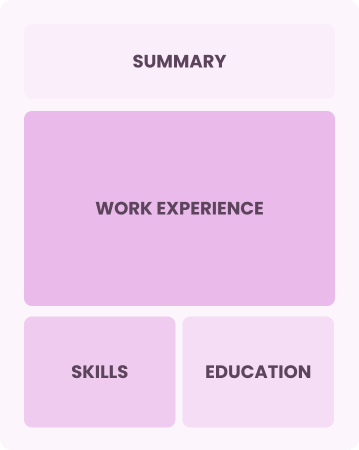

Resume Format Examples

Choosing the right resume format is important for design engineers, as it highlights key skills, relevant experience, and career growth effectively to potential employers.

Functional

Focuses on skills rather than previous jobs

Best for:

Recent graduates and career changers with limited experience in design engineering

Combination

Balances skills and work history equally

Best for:

Mid-career professionals eager to highlight their skills and growth potential

Chronological

Emphasizes work history in reverse order

Best for:

Engineers leading innovative projects with extensive technical expertise

Frequently Asked Questions

Should I include a cover letter with my design engineer resume?

Absolutely, including a cover letter is essential for showcasing your unique qualifications and enthusiasm for the design engineer role. It allows you to highlight specific achievements and provide insight into your motivations. For assistance, consider our comprehensive guide on how to write a cover letter or use our Cover Letter Generator to get started quickly.

Can I use a resume if I’m applying internationally, or do I need a CV?

When applying for jobs abroad, use a CV instead of a resume as it is often the standard format. To ensure your CV meets international expectations, explore our extensive resources on how to write a CV tailored for global applications. Additionally, consider reviewing CV examples to understand different styles and structures that are effective internationally.

What soft skills are important for design engineers?

Soft skills such as interpersonal skills, communication, collaboration, and problem-solving are essential for design engineers. These abilities facilitate effective teamwork and enable engineers to understand client needs, leading to innovative solutions and successful project outcomes.

I’m transitioning from another field. How should I highlight my experience?

When transitioning to a design engineer role, highlight your transferable skills such as creativity, teamwork, and analytical thinking. These abilities demonstrate your potential to innovate and solve problems effectively. Use concrete examples from prior experiences to showcase how these strengths align with key engineering tasks and project requirements.

How should I format a cover letter for a design engineer job?

To format a cover letter for design engineer positions, begin with your contact details and a professional greeting. Follow this by crafting a compelling opening that emphasizes your interest in the role. Include a paragraph summarizing your key skills and experiences relevant to the job description. Finally, conclude with a strong closing statement encouraging the employer to reach out.

Should I include a personal mission statement on my design engineer resume?

Yes, including a personal mission statement on your resume is recommended. It highlights your values and design philosophy effectively, which is particularly useful for organizations that emphasize innovation and creativity in their culture.