Hard skills are technical capabilities such as skill in CAD software, material science knowledge, and project management that enable effective product design and development.

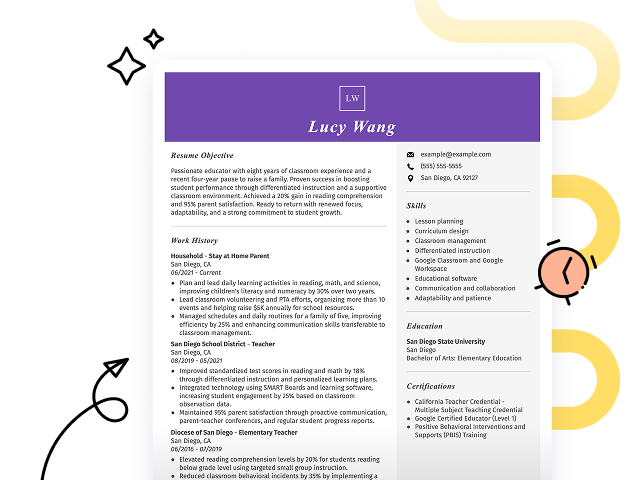

Popular Product Development Engineer Resume Examples

Check out our top product development engineer resume examples that emphasize critical skills such as design thinking, project management, and cross-functional collaboration. These examples demonstrate how to effectively showcase your accomplishments and attract potential employers.

Ready to build your standout resume? Our Resume Builder offers user-friendly templates specifically designed for engineering professionals, helping you make a strong impression in your job search.

Recommended

Entry-level product development engineer resume

This entry-level resume for a product development engineer effectively highlights the job seeker's design skills and achievements from previous roles, showcasing their ability to improve productivity and reduce costs. New professionals in this field must demonstrate strong project outcomes and relevant technical competencies through their resumes, even with limited industry experience.

Mid-career product development engineer resume

This resume effectively showcases the applicant's qualifications by illustrating their impact in previous roles, such as revenue generation and efficiency improvements. The strategic presentation of skills and accomplishments highlights their readiness for leadership positions and complex projects in product development.

Experienced product development engineer resume

This work experience section emphasizes the applicant's robust experience as a product development engineer, highlighting significant achievements such as reducing production costs by 15% and improving design efficiency by 20%. The clear formatting allows hiring managers to quickly identify key accomplishments across multiple roles.

Resume Template—Easy to Copy & Paste

Min Rodriguez

Cedar Valley, MN 55136

(555)555-5555

Min.Rodriguez@example.com

Skills

- Product Development

- CAD Modeling

- Process Engineering

- Cross-Functional Leadership

- Cost Reduction Strategies

- Design Optimization

- Rapid Prototyping

- Sustainability in Design

Languages

- Spanish - Beginner (A1)

- French - Intermediate (B1)

- German - Beginner (A1)

Professional Summary

Dynamic Product Development Engineer with 5 years' experience in creating innovative solutions and optimizing engineering processes. Proven track record in cost reduction and team leadership driving results.

Work History

Product Development Engineer

Innovative Tech Industries - Cedar Valley, MN

September 2022 - October 2025

- Developed 5 new products yearly, improving efficiency 20%.

- Led cross-functional teams resulting in 0k savings.

- Enhanced design processes, reducing time-to-market by 30%.

Product Design Engineer

TechSolutions Co. - Cedar Valley, MN

January 2020 - August 2022

- Streamlined software tools, boosting team productivity 25%.

- Implemented testing protocols, decreasing defects by 15%.

- Collaborated on launch of first eco-friendly product line.

Junior Product Engineer

NextGen Devices - Minneapolis, MN

January 2018 - December 2019

- Assisted in redesign of existing products, cutting costs 10%.

- Drafted detailed CAD models improving precision engineering.

- Analyzed customer feedback enhancing user satisfaction 18%.

Certifications

- Certified Product Manager - Product Management Institute

- Six Sigma Green Belt - Six Sigma Certification Board

Education

Master of Science Mechanical Engineering

University of California, Berkeley Berkeley, California

May 2018

Bachelor of Science Mechanical Engineering

Stanford University Stanford, California

June 2016

How to Write a Product Development Engineer Resume Summary

Your resume summary is the first impression you make on hiring managers, so it’s important to craft it carefully. As a product development engineer, you should emphasize your innovative skills and experience in bringing concepts to life, showcasing how you can contribute to developing cutting-edge products.

Highlight your technical expertise, teamwork capabilities, and problem-solving skills in this section. These traits are essential for creating successful products that meet market needs and exceed customer expectations.

To illustrate effective summaries, we will provide examples that demonstrate what makes a strong resume summary for product development engineers:

I am a product development engineer with experience and skills in designing and improving products. I am looking for a position where I can use my abilities to help the company succeed. A job that offers flexibility and growth opportunities is very appealing to me. I believe I would be a great asset if given the chance.

- Lacks specific details about past projects or achievements, making it hard to evaluate expertise

- Relies heavily on personal aspirations instead of showcasing contributions to previous employers

- Uses generic phrases that do not highlight unique skills or strengths relevant to product development engineering

Innovative product development engineer with 7+ years of experience in designing and launching consumer electronics. Spearheaded the development of a new product line that increased market share by 20% within the first year, resulting in $2M in revenue growth. Proficient in CAD software, rapid prototyping techniques, and cross-functional team collaboration to drive product enhancements and ensure alignment with customer needs.

- Begins with clear indication of experience level and area of expertise

- Highlights quantifiable achievements that showcase significant business impact

- Mentions specific technical skills relevant to product development roles

Pro Tip

Showcasing Your Work Experience

The work experience section is important for your resume as a product development engineer, and it will contain the bulk of your content. Good resume templates reliably include this important section to emphasize your professional background.

Organized in reverse-chronological order, this area should list your previous positions clearly. Use bullet points to highlight key achievements and responsibilities that illustrate your contributions in each role effectively.

To give you a clearer picture, we’ve prepared a couple of examples that showcase effective work history entries for product development engineers. These examples will demonstrate what makes an entry stand out and what pitfalls to avoid:

Product Development Engineer

Innovate Tech Solutions – San Francisco, CA

- Helped design products.

- Collaborated with teams.

- Conducted tests on prototypes.

- Assisted in project documentation.

- Lacks specific accomplishments or impacts of the projects worked on

- Bullet points are vague and do not highlight unique skills or contributions

- Does not mention any measurable results from the product development efforts

Product Development Engineer

Innovative Solutions Inc. – San Francisco, CA

March 2020 - Current

- Lead the design and development of five new product lines, contributing to a 40% increase in market share within one year.

- Use user feedback and data analysis to refine product features, improving customer satisfaction ratings by 30%.

- Collaborate with cross-functional teams to streamline production processes, reducing costs by 15% while maintaining quality standards.

- Starts each bullet with powerful action verbs that highlight the job seeker's achievements

- Incorporates specific metrics to demonstrate the impact of the job seeker's contributions

- Showcases relevant skills and collaboration efforts essential for a product development engineer

While your resume summary and work experience are important components, don't overlook the significance of other sections that can improve your application. For detailed guidance on perfecting every part of your resume, be sure to explore our comprehensive guide on how to write a resume.

Top Skills to Include on Your Resume

A well-defined skills section is important for any resume, as it allows hiring managers to quickly assess if you possess the necessary qualifications. This section serves as a snapshot of your capabilities, helping you stand out in a competitive job market.

For a product development engineer, focus on highlighting technical skills, hard and soft skills. Mention relevant tools like CAD software, project management systems, and prototyping techniques to demonstrate your skill in the field.

Soft skills include creativity, problem-solving, and teamwork which facilitate innovative solutions and seamless collaboration in the engineering process.

Selecting the right resume skills is important for aligning with employer expectations and ensuring compatibility with automated screening systems. Many organizations use software to filter out job seekers lacking essential skills, making it important to tailor your resume accordingly.

To improve your chances, carefully review job postings for insights into which skills are most valued by recruiters and ATS systems. By focusing on these specific skills, you can create a targeted resume that stands out in the hiring process.

Pro Tip

10 skills that appear on successful product development engineer resumes

To capture the attention of recruiters, it's essential to highlight in-demand skills that align with product development engineering. You can find these skills reflected in our resume examples to ensure a well-crafted resume.

Here are 10 skills you may want to include in your resume if they align with your qualifications and job specifications:

Problem-solving

Project management

Technical skill

Collaboration

Attention to detail

Data analysis

Creative thinking

Prototyping

Agile methodology

Knowledge of CAD software

Based on analysis of 5,000+ engineering professional resumes from 2023-2024

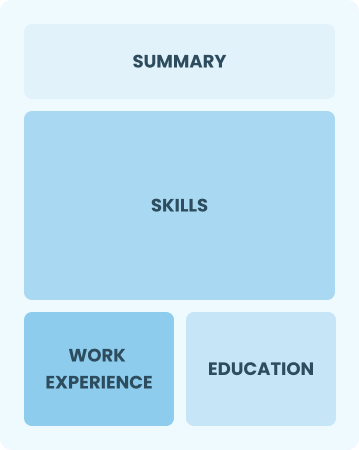

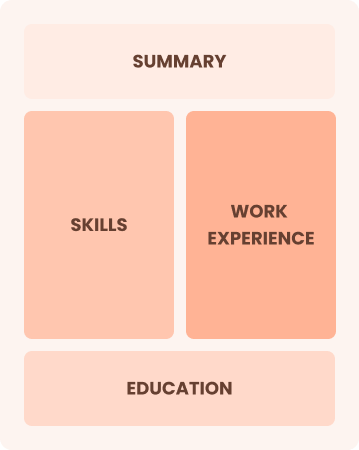

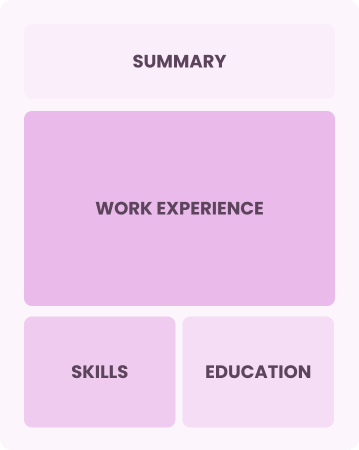

Resume Format Examples

Selecting the appropriate resume format is important for a product development engineer as it clearly showcases your technical skills, project experience, and growth.

Functional

Focuses on skills rather than previous jobs

Best for:

Recent graduates and career changers with limited experience in product development

Combination

Balances skills and work history equally

Best for:

Mid-career professionals focused on demonstrating their skills and seeking growth opportunities

Chronological

Emphasizes work history in reverse order

Best for:

Engineers leading innovative product solutions with extensive industry expertise

Frequently Asked Questions

Should I include a cover letter with my product development engineer resume?

Including a cover letter can significantly improve your application by showcasing your personality and detailing how your skills align with the job. It offers a unique opportunity to express your enthusiasm for the position. If you need assistance, explore our guide on how to write a cover letter or try our Cover Letter Generator for quick support.

Can I use a resume if I’m applying internationally, or do I need a CV?

When applying for jobs outside the U.S., use a CV instead of a resume when the employer specifically requests it or in regions where CVs are standard. For guidance, explore our resources on how to write a CV that provide tips on effective formatting and content creation. Additionally, review various CV examples to better understand what makes a strong CV.

What soft skills are important for product development engineers?

Soft skills like communication, collaboration, and problem-solving are essential for product development engineers. These interpersonal skills enable effective teamwork and foster innovation, allowing engineers to work closely with cross-functional teams and understand customer needs better.

I’m transitioning from another field. How should I highlight my experience?

Highlight your transferable skills such as project management, analytical thinking, and teamwork when applying for product development engineer roles. These abilities showcase your readiness to innovate and solve problems, even if your experience in engineering is limited. Share concrete examples from past positions that illustrate how you’ve successfully contributed to projects and driven results.

How should I format a cover letter for a product development engineer job?

To format a cover letter for product development engineer positions, start with your contact information and include a professional greeting. Create an engaging opening paragraph that highlights your interest in the role. Add a summary of your relevant skills and experiences customized to the job requirements. Wrap up with a compelling closing statement that encourages the employer to connect for further discussion.

How do I write a resume with no experience?

Job seekers aiming for product development engineer roles can benefit from resume with no experience strategies to highlight relevant coursework, internships, project work, and technical skills like CAD software skill. Emphasize problem-solving abilities and teamwork experiences gained from school projects or extracurricular activities. Remember, your enthusiasm and willingness to learn can make a lasting impression on employers.