Hard skills involve a strong skill in design verification methodologies, using tools like UVM and SystemVerilog to ensure the seamless operation of complex systems.

Popular Design Verification Engineer Resume Examples

Discover our top design verification engineer resume examples that emphasize critical skills such as test planning, quality assurance, and technical documentation. These examples will help you showcase your expertise effectively to prospective employers.

Ready to build an impressive resume? Our Resume Builder offers user-friendly templates specifically designed for engineering professionals, making it simpler than ever to highlight your qualifications.

Recommended

Entry-level design verification engineer resume

This entry-level resume effectively showcases the job seeker's hands-on experience in design verification, highlighting significant achievements in both validation and efficiency improvements. New professionals in this field must demonstrate their technical competencies and collaborative skills through relevant project experiences and educational accomplishments to attract potential employers.

Mid-career design verification engineer resume

This resume effectively showcases essential qualifications by highlighting achievements such as efficiency gains and leadership in complex projects. The structured presentation of skills and experience indicates a applicant well-prepared for advanced design verification challenges and team roles.

Experienced design verification engineer resume

This resume highlights the applicant’s extensive expertise as a design verification engineer, demonstrating significant achievements such as increasing verification coverage by 30% and streamlining validation cycles by 20%. The bullet point format effectively showcases accomplishments for quick reference, benefiting technical hiring managers.

Resume Template—Easy to Copy & Paste

Michael Kim

Crestwood, KY 40019

(555)555-5555

Michael.Kim@example.com

Professional Summary

Results-driven Design Verification Engineer with 7 years in semiconductor industry, expertly reducing simulation time and enhancing chip quality employing SystemVerilog and UVM tools.

Work History

Design Verification Engineer

SiliconTech Innovations - Crestwood, KY

March 2024 - October 2025

- Led verification of complex SoC projects, boosting efficiency by 30%

- Reduced simulation time by 25% using advanced verification methods

- Enhanced design quality by implementing innovative debugging tools

Verification Specialist

MicroLogic Solutions - Louisville, KY

March 2021 - February 2024

- Developed custom scripts that improved testing speed by 40%

- Collaborated on DV projects leading to a 50% reduction in errors

- Optimized verification process, increasing test coverage by 20%

Junior Chip Designer

LogicWave Corp - Louisville, KY

March 2018 - February 2021

- Assisted in IC design projects, advancing timelines by 15%

- Performed testing protocols, reducing defects by 10%

- Implemented new design techniques improving yield by 5%

Skills

- SystemVerilog

- UVM Methodologies

- RTL Design

- FPGA Prototyping

- Functional Coverage

- Simulation Tools

- VLSI Design

- Python Scripting

Education

Masters Electrical Engineering

California Institute of Technology Pasadena, California

May 2017

Bachelors Computer Engineering

University of California, Berkeley Berkeley, California

May 2014

Certifications

- Certified Verification Engineer - Institute of Electrical and Electronics Engineers

- Advanced FPGA Design - Digital Design Authority

Languages

- Spanish - Beginner (A1)

- Mandarin - Beginner (A1)

- German - Intermediate (B1)

How to Write a Design Verification Engineer Resume Summary

Your resume summary is the first opportunity to make a lasting impression on hiring managers, so it’s important to craft it thoughtfully. As a design verification engineer, you should highlight your technical skills and experience in ensuring product compliance with specifications and standards. The following examples will illustrate effective strategies for creating compelling summaries that capture your qualifications:

I am a design verification engineer with several years of experience and a solid educational background. I want to find a position that allows me to use my skills in a supportive environment. A job that offers learning opportunities and good work-life balance would be the best fit for me. I believe I can contribute positively if given the chance.

- Lacks specific details about the applicant’s accomplishments or technical skills relevant to design verification

- Overuses personal language, making it feel less professional and more like filler

- Emphasizes what the job seeker seeks in a job rather than showcasing their potential value to an employer

Results-driven design verification engineer with 7+ years of experience in the aerospace industry, specializing in system-level testing and validation. Improved product reliability by 20% through rigorous testing protocols and automated verification processes. Proficient in MATLAB, Simulink, and hardware-in-the-loop (HIL) simulations, with a strong background in cross-functional team collaboration to ensure compliance with industry standards.

- Begins with specific years of experience and industry specialization

- Highlights quantifiable achievements that showcase a direct impact on product quality

- Mentions relevant technical skills important for the role, improving appeal to potential employers

Pro Tip

Showcasing Your Work Experience

The work experience section is the cornerstone of your resume as a design verification engineer. This is where you’ll present the bulk of your qualifications, and good resume templates will always emphasize this important part.

In this section, list your previous positions in reverse-chronological order. Use bullet points to clearly articulate your achievements and responsibilities in each role, making it easy for hiring managers to gauge your contributions.

Let’s now look at a couple of examples that highlight effective work history entries for design verification engineers. These illustrations will clarify what makes an impact and what pitfalls to avoid:

Design Verification Engineer

Tech Innovations Inc. – San Francisco, CA

- Reviewed designs for compliance.

- Collaborated with team members.

- Conducted testing and analysis.

- Created reports on findings.

- No details about the employment dates

- Bullet points are vague and lack specific achievements

- Emphasizes routine tasks instead of compelling contributions

Design Verification Engineer

Tech Solutions Inc. – San Francisco, CA

March 2020 - Present

- Lead verification efforts for complex electronic systems, ensuring compliance with industry standards and achieving a 30% reduction in time-to-market.

- Develop comprehensive test plans and automated scripts that improved testing efficiency by 40%, improving product reliability.

- Collaborate with cross-functional teams to identify and resolve design issues early in the development cycle, contributing to a significant decrease in project delays.

- Starts each bullet with strong action verbs that clearly highlight contributions

- Incorporates quantifiable outcomes to showcase the job seeker's effectiveness and impact on projects

- Demonstrates relevant technical skills while emphasizing collaboration and problem-solving abilities

While your resume summary and work experience are important components, it's important not to overlook other sections that contribute to a strong application. Each part plays a role in presenting your qualifications effectively. To ensure you're covering all bases, be sure to check our comprehensive guide on how to write a resume.

Top Skills to Include on Your Resume

A skills section is important on your resume as it quickly showcases your qualifications to potential employers. It highlights what you bring to the table, setting you apart from other applicants.

As a design verification engineer, focus on technical skills like skill in verification tools such as Cadence and Synopsys. Additionally, knowledge of software like MATLAB or SystemVerilog can greatly improve your appeal to hiring managers.

Soft skills require effective communication and teamwork to collaborate with cross-functional teams, ensuring designs meet rigorous specifications and industry standards.

Selecting the right resume skills is important, as it helps align your qualifications with what employers expect from a job seeker. Many organizations use automated screening systems that filter out applicants lacking essential skills for the role.

To improve your chances of being noticed, carefully review job postings to identify key skills emphasized by recruiters. This approach ensures you prioritize relevant abilities, making your resume more appealing to both human readers and ATS algorithms.

Pro Tip

10 skills that appear on successful design verification engineer resumes

Stand out to hiring managers by showcasing the most sought-after skills for design verification engineers. You can find these skills highlighted in our resume examples, giving you the confidence to apply for positions that match your qualifications.

Here are 10 essential skills to consider adding to your resume if they align with your experience and job criteria:

Attention to detail

Problem-solving

Technical skill in verification tools

Knowledge of design processes

Collaboration and teamwork

Documentation skills

Analytical thinking

Project management

Familiarity with regulatory standards

Communication

Based on analysis of 5,000+ engineering professional resumes from 2023-2024

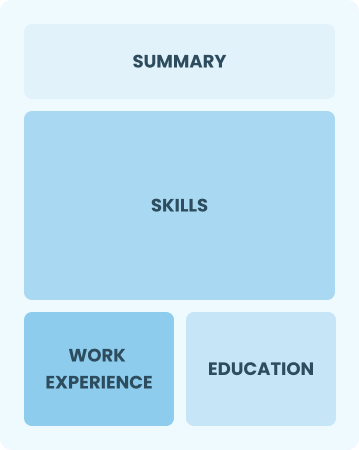

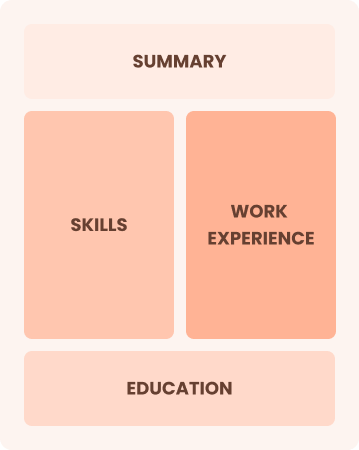

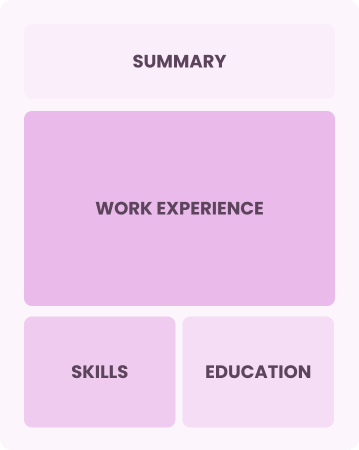

Resume Format Examples

Selecting the appropriate resume format is important for showcasing your design verification expertise, helping your key skills and career achievements stand out to potential employers.

Functional

Focuses on skills rather than previous jobs

Best for:

Recent graduates and career changers with up to two years of experience

Combination

Balances skills and work history equally

Best for:

Mid-career professionals focused on demonstrating their skills and pursuing growth opportunities

Chronological

Emphasizes work history in reverse order

Best for:

Seasoned engineers excelling in complex design challenges and team leadership

Frequently Asked Questions

Should I include a cover letter with my design verification engineer resume?

Absolutely, including a cover letter can significantly improve your application. It allows you to showcase your personality and explain how your skills align with the job requirements. For tips on crafting an effective cover letter, consider checking out our comprehensive guide on how to write a cover letter or use our Cover Letter Generator for quick assistance.

Can I use a resume if I’m applying internationally, or do I need a CV?

When applying for jobs abroad, use a CV instead of a resume as it is commonly preferred in many regions. Explore CV examples to see how to structure your document and review tips on how to write a CV that aligns with international expectations.

What soft skills are important for design verification engineers?

Soft skills such as interpersonal skills, communication, problem-solving, and teamwork are essential for design verification engineers. These abilities foster collaboration with cross-functional teams and ensure clear reporting of findings, leading to improved product quality and successful project outcomes.

I’m transitioning from another field. How should I highlight my experience?

Highlight your transferable skills, such as analytical thinking, teamwork, and attention to detail, when applying for design verification engineer positions. These abilities can showcase your adaptability and readiness to add value, even if you lack direct experience in the field. Use concrete examples from past roles to illustrate how your strengths align with the responsibilities of this position.

How should I format a cover letter for a design verification engineer job?

To format a cover letter for design verification engineer positions, begin with your contact details and follow with a warm greeting. Craft an engaging introduction that highlights your passion for the role, and summarize your relevant skills clearly. Always customize your content to align with the job requirements, and conclude with a strong call to action encouraging further discussion.

How do I add my resume to LinkedIn?

To increase your resume's visibility on LinkedIn, you should add your resume to LinkedIn by uploading it directly to your profile. Alternatively, include essential skills and achievements in the "About" and "Experience" sections. This approach helps recruiters find qualified design verification engineers more easily, improving your chances of being noticed for relevant opportunities.