Hard skills are technical abilities such as programming in languages like C and C++, debugging, and familiarity with embedded systems design that an embedded software engineer must possess.

Popular Embedded Software Engineer Resume Examples

Check out our top embedded software engineer resume examples that emphasize critical skills such as coding skill, system optimization, and problem-solving. These examples will help you showcase your technical achievements effectively.

Ready to build your ideal resume? Our Resume Builder offers user-friendly templates designed specifically for tech professionals, making it simple to highlight your expertise.

Recommended

Entry-level embedded software engineer resume

This entry-level resume effectively highlights the applicant's technical skills and accomplishments in embedded systems, emphasizing their hands-on experience with software development and optimization. New professionals should demonstrate a strong foundation in relevant programming languages and project outcomes to attract employers, even when their professional experience may be limited.

Mid-career embedded software engineer resume

This resume effectively showcases key qualifications by highlighting significant achievements and leadership roles. The clear presentation of skills and relevant experiences illustrates a solid career trajectory, indicating readiness for more complex challenges in embedded systems engineering.

Experienced embedded software engineer resume

This resume illustrates the applicant's robust experience in embedded software engineering, showcasing significant achievements like reducing execution time by 20% and leading a project that came in under budget by $15k. The bullet point formatting improves clarity, allowing hiring managers to quickly identify key accomplishments.

Resume Template—Easy to Copy & Paste

David Liu

Chicago, IL 60607

(555)555-5555

David.Liu@example.com

Professional Summary

Experienced Embedded Software Engineer skilled in IoT and real-time systems, with 8 years optimizing efficiency and enhancing security for innovative projects leading to cost savings.

Work History

Embedded Software Engineer

InnovateTech Solutions - Chicago, IL

October 2022 - October 2025

- Developed real-time systems for IoT devices.

- Reduced system latency by 15% through optimization.

- Implemented secure firmware updates saving 200K

Firmware Developer

NextGen MicroSystems - Chicago, IL

February 2019 - September 2022

- Optimized embedded code, boosting efficiency to 98%.

- Collaborated on innovative projects with cross-functional teams.

- Enhanced boot times by 20% via efficient coding.

Embedded Systems Specialist

TechCore Solutions - Springfield, IL

June 2017 - January 2019

- Led a team to design lightweight embedded apps.

- Improved software testing times by 25% using automation.

- Secured systems by implementing encryption protocols.

Languages

- Spanish - Beginner (A1)

- German - Intermediate (B1)

- Mandarin - Beginner (A1)

Skills

- C/C++ Programming

- Real-Time Systems

- Optimization Techniques

- IoT Devices

- Microcontrollers

- Firmware Development

- Embedded Linux

- Software Testing

Certifications

- Certified Embedded Systems Engineer - Embedded Systems Institute

- IoT Security Specialist - International IoT Association

Education

Master of Science Computer Engineering

Stanford University Stanford, California

May 2016

Bachelor of Science Electrical Engineering

University of California, Berkeley Berkeley, California

May 2014

How to Write a Embedded Software Engineer Resume Summary

Your resume summary is the first impression employers have, making it important to showcase your skills and experience. As an embedded software engineer, you should highlight your technical expertise, problem-solving abilities, and familiarity with various programming languages.

In this competitive field, it's important to demonstrate how your background aligns with the job requirements. Focus on relevant projects and accomplishments that set you apart from other applicants.

To guide you in crafting a standout summary, we will look at examples that illustrate what works well and what doesn’t in this key section:

I am an experienced embedded software engineer with a diverse background in software development. I seek a position where I can apply my skills and grow professionally. A company that values innovative ideas and offers a good work environment is what I’m looking for. I believe I would be a great asset if given the chance.

- Lacks specific examples of technical skills or projects that highlight expertise in embedded systems

- Overuses personal language, which detracts from professionalism and focus on value to potential employers

- Emphasizes personal career goals rather than detailing how the applicant’s contributions can benefit the organization

Detail-oriented embedded software engineer with 7+ years of experience in developing and optimizing firmware for consumer electronics. Achieved a 20% reduction in power consumption through innovative coding strategies and hardware integration, improving product efficiency. Proficient in C/C++, RTOS, and IoT protocols, with a strong focus on debugging and performance tuning.

- Begins with a specific experience level and area of expertise

- Highlights quantifiable achievements that showcase direct impact on product performance

- Lists relevant technical skills essential for embedded software engineering roles

Pro Tip

Showcasing Your Work Experience

The work experience section is important for your resume as an embedded software engineer, where you'll present most of your qualifications. Good resume templates emphasize this area to ensure it stands out.

This section should be organized in reverse-chronological order, listing your previous positions clearly. Use bullet points to highlight your key achievements and the impact you've made in each role.

To help you craft this section effectively, we will provide a couple of examples that illustrate what works well and what doesn't:

Embedded Software Engineer

Tech Innovations Inc. – Austin, TX

- Wrote code for embedded systems.

- Tested software on devices.

- Collaborated with team members on projects.

- Fixed bugs and updated software.

- Lacks specific employment dates to provide context

- Bullet points are too vague and do not highlight unique skills or contributions

- Focuses on basic tasks rather than showcasing powerful results or achievements

Embedded Software Engineer

Tech Innovations Inc. – San Francisco, CA

March 2020 - Present

- Developed embedded systems for IoT devices, increasing product efficiency by 30% through optimized firmware solutions.

- Collaborated with hardware teams to troubleshoot and improve system integration, reducing time-to-market by 15%.

- Mentored junior engineers in coding best practices and debugging techniques, improving team productivity and skill growth.

- Starts each bullet with effective action verbs that illustrate the job seeker's contributions

- Incorporates specific metrics demonstrating the job seeker's positive impact on projects

- Highlights relevant technical skills while showcasing teamwork and leadership efforts

While your resume summary and work experience are important, you shouldn't overlook the other sections that contribute to a polished presentation. For more in-depth guidance on crafting a standout resume, be sure to explore our comprehensive guide on how to write a resume.

Top Skills to Include on Your Resume

A well-defined skills section is important for your resume because it allows you to succinctly showcase your qualifications to potential employers. Including technical skills in this section helps employers quickly determine if you have the abilities required for the embedded software engineer role.

In this field, emphasize technical skills such as expertise in C/C++, familiarity with real-time operating systems, and hands-on experience with debugging tools like GDB. Highlighting your knowledge of embedded systems design and development will help distinguish you from other job seekers.

Soft skills include problem-solving, teamwork, and effective communication, which are essential for collaborating with cross-functional teams to develop innovative solutions.

Selecting the right resume skills is important because it helps align your qualifications with what employers expect. Many organizations use automated systems to filter out job seekers who lack essential skills for the position.

To improve your chances, review job postings carefully for insights on which skills are in demand. This approach will not only attract recruiters' attention but also ensure your resume meets ATS criteria effectively.

Pro Tip

10 skills that appear on successful embedded software engineer resumes

Highlighting key skills on your resume can significantly grab the attention of recruiters looking for embedded software engineers. Our resume examples showcase these essential skills in action, providing you with a competitive edge in your job applications.

Here are 10 essential skills to consider including in your resume if they align with your experience and job requirements:

C programming

Embedded systems design

Real-time operating systems (RTOS)

Debugging techniques

Software development life cycle (SDLC)

Version control systems

Microcontroller programming

Communication protocols (e.g., I2C, SPI)

Low-level hardware interaction

Problem-solving abilities

Based on analysis of 5,000+ engineering professional resumes from 2023-2024

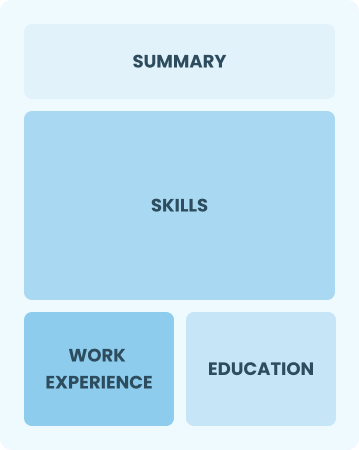

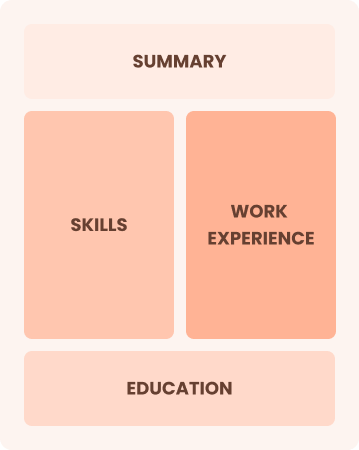

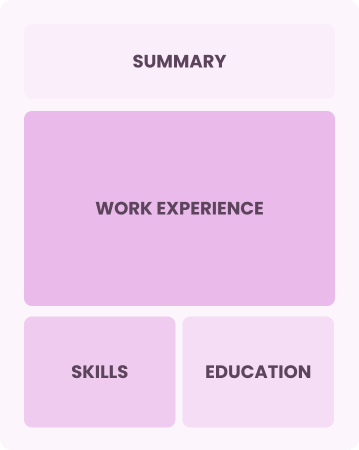

Resume Format Examples

Choosing the right resume format is important for an embedded software engineer. It showcases your technical skills and relevant experience clearly, helping potential employers recognize your career growth effectively.

Functional

Focuses on skills rather than previous jobs

Best for:

Recent graduates and career changers with up to two years of experience

Combination

Balances skills and work history equally

Best for:

Mid-career professionals focused on demonstrating their technical skills and growth potential

Chronological

Emphasizes work history in reverse order

Best for:

Experts leading innovative projects in embedded systems development

Frequently Asked Questions

Should I include a cover letter with my embedded software engineer resume?

Absolutely. Including a cover letter can significantly improve your application by highlighting your qualifications and demonstrating your enthusiasm for the position. It’s an excellent opportunity to connect your skills to the job requirements. For tips on crafting a compelling cover letter, explore our resources on how to write a cover letter. Alternatively, you can use our Cover Letter Generator for quick assistance.

Can I use a resume if I’m applying internationally, or do I need a CV?

When applying for jobs abroad, opt for a CV instead of a resume, as many regions prefer this format. To assist you, we offer resources that outline how to write a CV with effective formatting and creation techniques tailored to international standards. Additionally, you can explore various CV examples to guide you in crafting your own document.

What soft skills are important for embedded software engineers?

Soft skills like collaboration, problem-solving, and interpersonal skills are essential for embedded software engineers. These abilities foster teamwork and facilitate clear discussions about complex ideas, ultimately leading to successful project outcomes and strong working relationships within tech teams.

I’m transitioning from another field. How should I highlight my experience?

Highlight transferable skills such as analytical thinking, teamwork, and project management when applying for embedded software engineer roles. Even if your previous experience is in a different field, these skills can showcase your ability to tackle complex engineering challenges. Use concrete examples from past projects to illustrate how you can add value in this new position.

How do I write a resume with no experience?

If you’re aiming for an embedded software engineer position but lack extensive work experience, consider using a resume with no experience to highlight relevant projects, coursework, or internships. Emphasizing your programming skills, problem-solving abilities, and any collaborative work can make a significant impact. Remember, your passion for technology and eagerness to learn can resonate with employers and showcase your potential.

How do I add my resume to LinkedIn?

To increase your resume's visibility on LinkedIn, you can add your resume to LinkedIn directly or highlight important skills and projects in the "About" and "Experience" sections. This approach helps recruiters find qualified embedded software engineers like you, showcasing your expertise and making connections easier.